Mail:info@anke-pcb.com

WhatApp/WeChat: 008618589033832

Skype: sannyduanbsp

Drie aspecten om de machtsintegriteit te beveiligen inPCB ontwerpen

In het moderne elektronische ontwerp is Power Integrity een onmisbaar onderdeel van het PCB -ontwerp. Om de stabiele werking en prestaties van elektronische apparaten te waarborgen, moeten we de stroombron naar de ontvanger volledig overwegen en ontwerpen.

Door zorgvuldig het ontwerpen en optimaliseren van stroommodules, binnenste laagvliegtuigen en voedingschips kunnen we echt vermogensintegriteit bereiken. Dit artikel zal ingaan op deze drie belangrijke aspecten om praktische richtlijnen en strategieën te bieden voor PCB -ontwerpers.

I. Layout -bedrading van de stroommodule

De vermogensmodule is de energiebron van alle elektronische apparaten, de prestaties en lay -out beïnvloeden direct de stabiliteit en efficiëntie van het gehele systeem. De juiste lay -out en routering kunnen niet alleen de interferentie van ruis verminderen, maar ook zorgen voor een gladde stroomstroom, waardoor de algehele prestaties worden verbeterd.

2. Power -module lay -out

1. SOORSCHAPPERVERWERKING:

De Power Module moet speciale aandacht krijgen, omdat deze het startpunt van de kracht dient. Om de introductie van het geluid te verminderen, moet de omgeving rond de stroommodule zo schoon mogelijk worden gehouden om aangrenzen aan andere te voorkomenhoogfrequentof ruisgevoelige componenten.

2. Close op de voedingschip:

De stroommodule moet zo dicht mogelijk bij de aan stroom geleverde chip worden geplaatst. Dit kan verliezen in het huidige transmissieproces verminderen en de gebiedsvereisten van het binnenste laagvlak verminderen.

3. Verheer overwegingen van dissipatie:

De vermogensmodule kan tijdens de werking warmte genereren, dus er moet worden gewaarborgd dat er geen obstakels erboven zijn voor warmtedissipatie. Indien nodig kunnen koellichamen of fans worden toegevoegd voor het koelen.

4. Lussen vermijden:

Vermijd het vormen van stroomlussen om de mogelijkheid van elektromagnetische interferentie te verminderen.

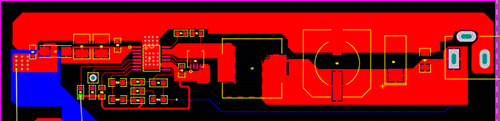

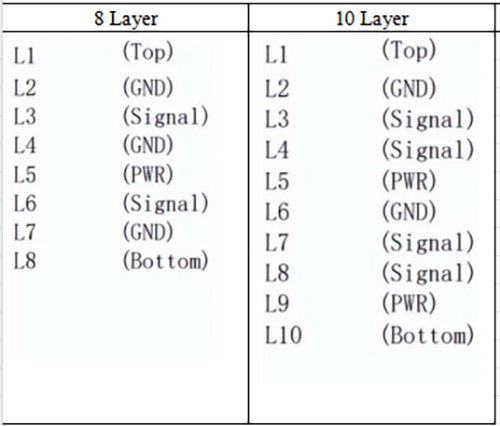

II. Binnenlaag Planning Planning

A. Laagstapelontwerp

In PCB EMC -ontwerp, Layer Stack Design is een belangrijk element dat moet overwegen routing en stroomverdeling.

A. Om te zorgen voor lage impedantie -eigenschappen van het vermogensvlak en de koppeling van de grondgeluids te absorberen, mag de afstand tussen vermogen en grondvlakken niet groter zijn dan 10 miljoen, meestal aanbevolen om minder dan 5 miljoen te zijn.

B. Als een enkel vermogensvlak niet kan worden geïmplementeerd, kan een oppervlaktelaag worden gebruikt om het stroomvlak op te leggen. De nauw aangrenzende kracht en grondvlakken vormen een vliegtuigcondensator met minimale AC-impedantie en uitstekende hoogfrequente kenmerken.

C. Vermijd aangrenzende twee stroomlagen, vooral met grote spanningsverschillen, om ruiskoppeling te voorkomen. Indien onvermijdelijk, verhoogt u de afstand tussen de twee vermogenslagen zoveel mogelijk.

D. Referentievliegtuigen, met name vermogensreferentievlakken, moeten lage impedantie -eigenschappen handhaven en kunnen worden geoptimaliseerd door bypass -condensatoren en laagaanpassingen.

B. Multiple Power Segmentation

A. Voor specifieke stroombronnen in kleine afstand, zoals de kernwerkspanning van een bepaalde IC-chip, moet koper op de signaallaag worden gelegd om de integriteit van het vermogensvlak te waarborgen, maar vermijd het leggen van stroomkoper op de oppervlaktelaag om de ruisstraling te verminderen.

B. De selectie van segmentatiebreedte moet geschikt zijn. Wanneer de spanning groter is dan 12V, kan de breedte 20-30 miljoen zijn; Kies anders 12-20 miljoen. De segmentatiebreedte tussen analoge en digitale stroombronnen moet worden verhoogd om te voorkomen dat digitaal vermogen de analoge kracht verstoort.

C. Eenvoudige power -netwerken moeten op de routeringslaag worden voltooid en langere stroomnetwerken moeten filtercondensatoren toegevoegd hebben.

D. Het gesegmenteerde vermogensvlak moet regelmatig worden gehouden om onregelmatige vormen te voorkomen die resonantie en verhoogde vermogensimpedantie veroorzaken. Lange en smalle strips en haltervormige divisies zijn niet toegestaan.

C. Planfiltering

A. Het vermogensvlak moet nauw worden gekoppeld aan het grondvlak.

B. Voor chips met operationele frequenties van meer dan 500 MHz, vertrouwt zich voornamelijk op filtering van de vlakcondensator en gebruik ze een combinatie van condensatorfiltering. Het filteringseffect moet worden bevestigd door de simulatie van de krachtintegriteit.

C. Installeer inductoren voor het ontkoppelen van condensatoren op het bedieningsvlak, zoals verbreding van condensator -leads en toenemende condensator -vias, om ervoor te zorgen dat de stroomgrondimpedantie lager is dan de doelimpedantie.

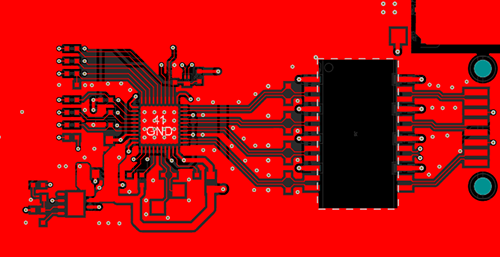

Iii. Koersklaver bedrading

De power chip is de kern van elektronische apparaten en ervoor zorgen dat de krachtintegriteit van de kracht cruciaal is voor het verbeteren van de prestaties en stabiliteit van het apparaat. Power Integrity Control for Power Chips omvat voornamelijk routingafhandeling van chip power pins en correcte lay -out en bedrading van ontkoppelingscondensatoren. Het volgende zal overwegingen en praktisch advies over deze aspecten beschrijven.

A.Chip Power Pin Routing

De routering van chip power pins is een cruciaal onderdeel van Power Integrity Control. Om een stabiele stroomvoorziening te bieden, wordt het aanbevolen om de routing van vermogenspennen te verdikken, in het algemeen tot dezelfde breedte als de chippennen. Meestal deminimale breedteMoet niet minder dan 8 miljoen zijn, maar probeer voor betere resultaten een breedte van 10 miljoen te bereiken. Door de routeringsbreedte te vergroten, kan de impedantie worden verminderd, waardoor de stroomgeluid wordt verminderd en voldoende stroomtoevoer naar de chip wordt gewaarborgd.

B. Layout en routing van ontkoppelingscondensatoren

Ontkoppelingscondensatoren spelen een belangrijke rol in de controle van de krachtintegriteit voor power chips. Afhankelijk van de condensatorkarakteristieken en toepassingsvereisten, zijn ontkoppelingscondensatoren over het algemeen onderverdeeld in grote en kleine condensatoren.

A. Grote condensatoren: grote condensatoren worden meestal gelijkmatig verdeeld over de chip. Vanwege hun lagere resonantiefrequentie en grotere filterradius kunnen ze effectief laagfrequente ruis filteren en een stabiele voeding bieden.

B. Kleine condensatoren: kleine condensatoren hebben een hogere resonantiefrequentie en kleinere filterradius, zodat ze zo dicht mogelijk bij de chippennen moeten worden geplaatst. Door ze te ver weg te plaatsen, kan het niet effectief filteren van hoogfrequente ruis, waardoor het ontkoppelingseffect wordt verloren. De juiste lay-out zorgt ervoor dat de effectiviteit van kleine condensatoren bij het filteren van hoogfrequente ruis volledig wordt gebruikt.

C. Onderstekende methode van parallelle ontkoppelingscondensatoren

Om de krachtintegriteit verder te verbeteren, zijn meerdere ontkoppelingscondensatoren vaak parallel aangesloten. Het belangrijkste doel van deze praktijk is om de equivalente serie -inductantie (ESL) van individuele condensatoren te verminderen door middel van parallelle verbinding.

Bij het parallel met meerdere ontkoppelingscondensatoren moet aandacht worden besteed aan de plaatsing van Vias voor condensatoren. Een gebruikelijke praktijk is om de vias van de kracht en de grond te compenseren. Het hoofddoel hiervan is om de wederzijdse inductantie tussen ontkoppelingscondensatoren te verminderen. Zorg ervoor dat de wederzijdse inductantie veel kleiner is dan de ESL van een enkele condensator, zodat de totale ESL -impedantie na parallel met meerdere ontkoppelingscondensatoren 1/n is. Door wederzijdse inductantie te verminderen, kan de filterefficiëntie effectief worden verbeterd, waardoor een verbeterde stroomstabiliteit wordt gewaarborgd.

Lay -outen routing van stroommodules, binnenste planningplanning van het laagvlak en de correcte afhandeling van power chip lay -out en bedrading zijn onmisbaar in het ontwerp van elektronisch apparaat. Door de juiste lay -out en routing kunnen we zorgen voor de stabiliteit en efficiëntie van vermogensmodules, het verminderen van ruisinterferentie en de algehele prestaties verbeteren. Laagstapelontwerp en meervoudige stroomsegmentatie optimaliseren de kenmerken van stroomvlakken verder, waardoor de interferentie van de stroomruis wordt verminderd. De juiste afhandeling van de lay -out en bedrading en ontkoppelingscondensatoren van de stroomschip zijn cruciaal voor de controle van de stroomintegriteit, waardoor een stabiele stroomvoorziening en effectieve ruisfiltering, het verbeteren van de prestaties en stabiliteit van het apparaat worden gewaarborgd.

In het praktische werk moeten verschillende factoren zoals de huidige grootte, routebreedte, het aantal vias, koppelingseffecten, enz., Worm volledig worden overwogen om rationele lay -out- en routeringsbeslissingen te nemen. Volg ontwerpspecificaties en best practices om controle en optimalisatie van stroomintegriteit te waarborgen. Alleen op deze manier kunnen we een stabiele en efficiënte voeding bieden voor elektronische apparaten, voldoen aan de toenemende prestatievereisten en de ontwikkeling en voortgang van elektronische technologie stimuleren.

Shenzhen Anke PCB Co., Ltd

Posttijd: Mar-25-2024